.jpg)

division, modulo are only synthesizable when the second operator is power of 2Negative numbers in twos-complement code endmodulemodule keywordmodule namePort list(without type)endmodulekeywordPort typesīit operations~, &, |, ^, ~^ (negate, and, or, xor, xnor)Bitwise operator on vectors, e.g.:4b1101 & 4b0110 = 4b0100If the operand widths are not equal, the smaller one is extended with zeros2b11 & 4b1101 = 4b0001(Logic operators: !, &, ||)īit reduction operatorsOperates on all bits of a vector, the output is a single bit&, ~&, |, ~|, ^, ~^ (and, nand, or, nor, xor, xnor) &4b1101 = 1b0|4b1101 = 1b1Typical usage scenarios: Parity checkĬomparisonSame as in CEqual, not-equal=, !=: equality considering Z, X!=: not-equal considering Z, XComparison, =ĪrithmeticSame as in COperators: +, -, *, /, %Not all of them is synthesizableE.g. Verilog: modulemodule test(clk, data_in, data_out, valid) input clk input data_in output data_out output reg valid. Verilog: module (2001)module keywordmodule nameInput portsOutput portsendmodulekeywordFunctional descriptionmodule test(input clk,input data_in,output data_out,output reg valid). Verilog SyntaxComments (like C)//one line/* */multiple linesConstantsĥb00100:00100 decimal value: 4, 5 bit wide8h4e:01001110 decimal value: 78, 8 bit wide4bZ:ZZZZ high impedance state

ModulesBuilding blocks to design complex, hierarchical systemsHierarchical description, partitioning

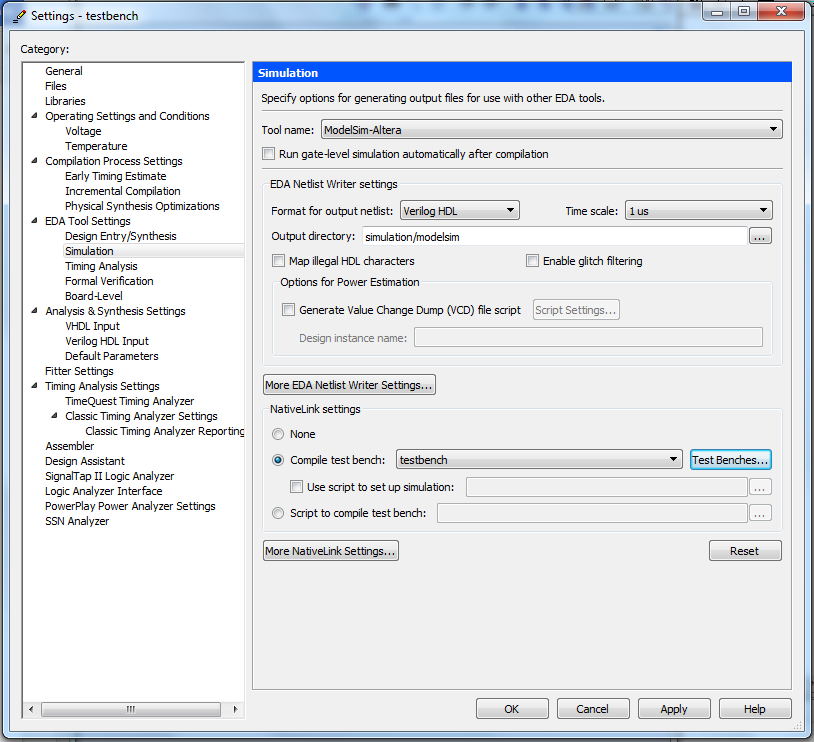

#Writememh in verilog modelsim altera software#

HDL languagesModular languagesHDL moduleInput and output port definitionsLogic equations between the inputs and the outputsUnlike software programming languages, NOT a sequential languageDescribes PARALLEL OPERATIONS Purpose of HDL languagesModeling hardware behaviorLarge part of these languages can only be used for simulation, not for hardware generation (synthesis)Synthesizable part depends on the actual synthesizerReplace graphical, schematic based design method (which very time consuming)RTL (Register Transfer Level) level descriptionAutomatic hardware synthesisIncrease productivity

Other HDL languagesHDL development is very time consuming compared to software developmentLot of programmers with C/C++ knowledge, much less HDL designerHigh level hardware description languagesCeloxica Handel-C: based on ANSI-C with special featuresSystemC: standardized, object oriented C++ based languageMentor Catapult-C: can generate hardware from standard C codeFaster simulation, verificationHW/SW co-design Standard HDL languagesStandards HDL (hardware description language) languagesVerilog1984: Gateway Design Automation Inc.1990: Cadence -> Open Verilog International1995: IEEE standardization2001: Verilog 2001VHDL1983-85: IBM, Texas Instruments1987: IEEE standardization1994: VHDL-1993

0 kommentar(er)

0 kommentar(er)